# **Digital Electronics EE(4<sup>th</sup> Sem B.Tech)**

# **Module-1**

## Fundamentals of Digital Systems and logic families

## ANALOG SIGNALS

We are very familiar with analog signals. The readings of a moving coil or moving iron voltmeter and ammeter, dynamometer wattmeter etc., are all analog quantities. The trace on a CRO screen is also analog. Analog methods for communication system have long been in use. Frequency division multiplexing is the means of analog communication. An electronic amplifier is an analog circuit. The low level analog signal (audio, video, etc.) is amplified to provide strength to the signal. Analog circuit systems (position control, process control) have been in use for the past many decades. Analog Computers use voltages, resistances and potentiometric rotations to represent the numbers and perform arithmetic operations. Analog differentiation, integration, etc., is also done. Operational amplifier is a very versatile analog electronic circuit used to perform a variety of operations (addition, subtraction, multiplication, division, exponentiation, differentiation, integration etc.). Analog integrated circuits are widely used in electronic industry.

## DIGITAL SIGNALS

The term digital is derived from digits. Any device or system which works on digits is a digital device or system. A digital voltmeter indicates the value of voltage in the form of digits, e.g., 230.25. Reading an analog instrument introduces human error and also requires more time. A digital reading is more accurate, eliminates human error and can be read quickly. Communication systems have also gone digital. The initial signal waveform is always analog. To use digital transmission, the signal waveform is sampled and the digital representation transmitted.

## **BASIC DIGITAL CIRCUITS**

In a digital system there are only a few basic operations performed, irrespective of the complexities of the system. These operations may be required to be performed a number of times in a large digital system like digital computer or a digital control system, etc. The basic operations are AND, OR, NOT, and FLIP-FLOP. The AND, OR, and NOT operations are discussed here and the FLIP-FLOP, which is a basic memory element used to store binary information (one bit is stored in one FLIP-FLOP).

#### The AND Operation

A circuit which performs an AND operation is shown in Fig. It has N inputs (N = 2) and one output. Digital signals are applied at the input terminals marked A, B, ..., N, the other terminal being ground, which is not shown in the diagram. The output is obtained at the output terminal marked Y (the other terminal being ground) and it is also a digital signal. The AND operation is defined as : the output is 1 if and only if all the inputs are 1. Mathematically, it is written as

| I | nputs | Output |

|---|-------|--------|

| A | В     | Y      |

| 0 | 0     | 0      |

| 0 | 1     | 0      |

| 1 | 0     | 0      |

| 1 | 1     | 1      |

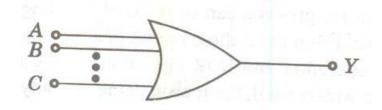

## The OR Operation

Figure below shows an OR gate with N inputs (N  $\ge$  2) and one output. The OR operation is defined as: the output of an OR gate is 1 if and only if one or more inputs are 1. Its logical equation is given by

$Y = A OR B OR C \dots OR$   $N = A + B + C + \dots + N$

|   | Inputs | Output |

|---|--------|--------|

| A | В      | Y      |

| 0 | 0      | 0      |

| 0 | 1      | 0      |

| 1 | 0      | 0      |

| 1 | 1      | 1      |

|   |        |        |

#### The NOT Operation

Figure below shows a NOT gate, which is also known as an *inverter*. It has one input (A) and one output (Y). Its logic equation is written as

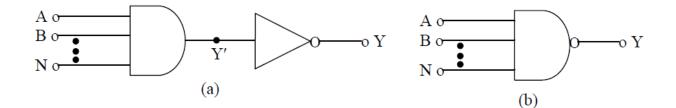

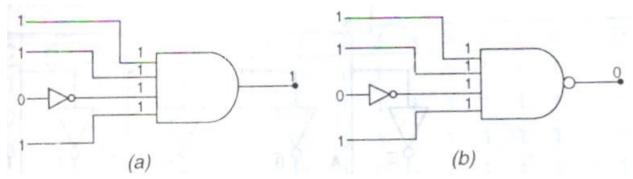

## The NAND Operation

The NOT-AND operation is known as the NAND operation. Figure shows and N input (N  $\geq$  2) AND gate followed by a NOT gate. The operation of this circuit can be described in the following way:

The output of the AND gate (Y') can be written using Eq.

$$Y' = AB \dots N$$

Now, the output of the NOT gate (Y) can be written using Eq.

Y = Y' = (AB...N)

| Inputs |   | Output |

|--------|---|--------|

| A      | В | Y      |

| 0      | 0 | 0      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 1      |

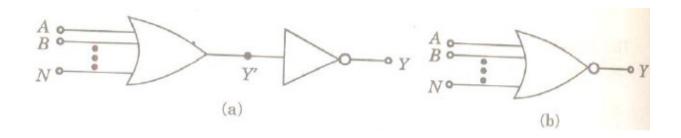

## The NOR Operation

The NOT-OR operation is known as the NOR operation. Figure below shows an N input (N  $\geq$  2) OR gate followed by a NOT gate. The operation of this circuit can be described in the following way:

The output of the OR gate Y' can be written using Eq. as

$$\mathbf{Y'}_{\cdot} = \mathbf{A} + \mathbf{B} + \ldots + \mathbf{N}$$

and the output of the NOT gate (Y) can be written using Eq.

$$Y = Y' = A + B + \dots + N$$

| Inputs |   | Output |

|--------|---|--------|

| A      | В | Y      |

| 0      | 0 | 0      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 1      |

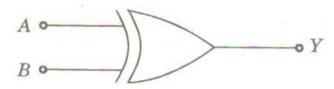

## **EXCLUSIVE-OR OPERATION**

The EXCLUSIVE-OR (EX-OR) operation is widely used in digital circuits. It is not a basic operation and can be performed using the basic gates-AND, OR and NOT or universal gates NAND or NOR. Because of its importance, the standard symbol shown below is used for this operation.

| Inputs |   | Output |

|--------|---|--------|

| A      | В | Y      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 0      |

## **BOOLEAN ALGEBRA**

**Commutative Law**

$$\mathbf{A} + \mathbf{B} = \mathbf{B} + \mathbf{A}$$

$A \cdot B = B \cdot A$

The above two equations mean that inputs can be interchanged in OR gate and AND gate.

Associative Law

$$A + (B + C) = (A + B) + C$$

A. (B. C) = (A. B) C

**Distributive Law**

$$A + (B. C) = (A + B). (A + C)$$

A.  $(B + C) = A. B + A. C$

## **DE MORGAN'S THEOREMS**

First Theorem : DE Morgan's first theorem is

Ā  $\overline{A}.\overline{B}$ Β  $\overline{A + B}$ В А

Second Theorem : De Morgan's second theorem can be written as

$$AB = \overline{A} + \overline{B}$$

| А | В | Ā | $\overline{\mathrm{B}}$ | AB | $\overline{AB}$ | $\overline{A} + \overline{B}$ |

|---|---|---|-------------------------|----|-----------------|-------------------------------|

| 0 | 0 | 1 | 1                       | 0  | 1               | 1                             |

| 0 | 1 | 1 | 0                       | 0  | 1               | 1                             |

| 1 | 0 | 0 | 1                       | 0  | 1               | 1                             |

| 1 | 1 | 0 | 0                       | 1  | 0               | 0                             |

$$A + B = \overline{A}, \overline{B}$$

#### **DECIMAL NUMBER SYSTEM**

We are all familiar with the decimal number system. It uses ten digits (0, 1, 2, 3, 4, 5, 6, 7, 9) and thus its base is 10. The decimal number system of counting was evolved because we have 8 fingers and 2 thumbs on our two hands so that we can count 10. By using the different digits in different positions we can express any number. For numbers bigger than 9 we use two or more digits. The position of each digit in the number indicates the magnitude that this number represents. In the number 27 the digit 7 represents  $7 \times 10^{\circ}$  or 7 and the digit 2 represents  $2 \times 10^{1}$  or 20. The sum of 7 and 20 makes 27. Similarly the number 263 can be expressed as Decimal  $263 = (2 \times 10^{2}) + (6 \times 10^{1}) + (3 \times 10^{0}) = 200 + 60 + 3 = 263$ . Since the base in decimal number system is 10, the number 263 can be written as  $263_{10}$ . The suffix 10 emphasizes the fact that the base is 10.

#### **BINARY NUMBER SYSTEM**

The binary number system has only two digits 0 and 1. Thus a binary number is a string of zeros and ones. Since it has only two digits, the base is 2. The abbreviation of binary digit is bit. The binary number 1100 has 4 bits, 101011 has 6 bits and 11001010 has 8 bits. Each bit may represent either 0 or 1. A string of 8 bits is known as a byte. A byte is the basic unit of data in computers. In most computers, the data is processed in strings of 8 bits or some multiples (i.e., 16, 24, 32 etc.). The computer memory also stores data in strings of 8 bits or multiples of 8 bits.

#### **Binary to Decimal Conversion**

The procedure to convert a binary number to decimal start with the left hand bit. Multiply this value by 2 and add the next bit. Again multiply by 2 and add the next bit. Stop when the bit on extreme right hand side is reached. Another fast and easy method to convert binary number to decimal number is as under:

- 1. Write the binary number.

- 2. Write the weights 2<sup>0</sup>, 2<sup>1</sup>, 2<sup>2</sup>, 2<sup>3</sup> etc., under the binary digits starting with the bit on right hand side.

- 3. Cross out weights under zeros.

- 4. Add the remaining weights.

**Example** Convert 100101<sub>2</sub> to decimal.

Solution : Left hand bit 1 Multiply by 2 and add next bit  $2 \times 1 + 0 = 2$ Multiply by 2 and add next bit  $2 \times 2 + 0 = 4$ Multiply by 2 and add next bit  $2 \times 4 + 1 = 9$ Multiply by 2 and add next bit  $2 \times 9 + 0 = 18$ Multiply by 2 and add next bit  $2 \times 18 + 1 = 37$

Therefore,  $100101_2 = 37_{10}$

#### **Decimal to Binary Conversion**

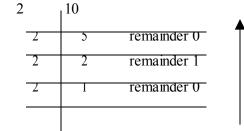

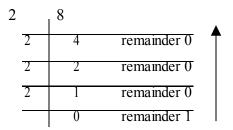

A systematic way to convert a decimal number into equivalent binary number is known as double dabble. This method involves successive division by 2 and recording the remainder (the remainder will be always 0 or 1). The division is stopped when we get a quotient of 0 with a remainder of 1. The remainders when read upwards give the equivalent binary number.

**Example 2.4** Convert decimal number 10 into its equivalent binary number.

0 remainder 1

The binary number is 1010.

#### SIGNED BINARY NUMBERS

To represent negative numbers in the binary system, digit 0 is used for the + sign and 1 for the -ve sign. The most significant bit is the sign bit followed by the magnitude bits. Numbers expressed in this manner are known as signed binary numbers. The numbers may be written in 4 bits, 8 bits, 16 bits, etc. In every case, the leading bit represents the sign and the remaining bits represent the magnitude.

**Example** Express in 16-bit signed binary system : (a) + 8, (b) -8, (c) 165, (d) -165. **Solution** : (a)

The binary number is 1000.

For the 16 bit system, we use 16 bits, 0 (which stands for +) in the leading position, 1000 in the last 4 bits and 0 in the remaining 11 positions. So the signed 16 bit binary number is

$+8 = 0000 \ 0000 \ 0000 \ 1000$

(b) In the leading bit we will have 1 (to represent the '-' sign). The rest of the representation is the same s in part (a).

#### **1'S COMPLEMENT**

The 1's complement of a binary number is obtained by complementing each bit (i.e., 0 for 1 and 1 for 0).

Thus each bit in the original word is inverted to give the 1's complement.

For

example, for the number

|                   | 1100 | 1001 |

|-------------------|------|------|

| 1's complement is | 0011 | 0110 |

#### **2'S COMPLEMENT**

The signed binary numbers required too much electronic circuitry for addition and subtraction. Therefore, positive decimal numbers are expressed in sign-magnitude form but negative decimal numbers are expressed in 2's complements.

2's complement is defined as the new word obtained by adding 1 to 1's complement\* e.g., Let  $A = 0 \ 1 \ 0 \ 1 \ i.e., 5$

## 1's complement of A is denoted by A and 2's complement of A is denoted by A'. **2'S COMPLEMENT ADDITION, SUBTRACTION**

The use of 2's complement representation has simplified the computer hardware\* for arithmetic operations. When A and B are to be added, the B bits are not inverted so that we get

$$S = A + B$$

When B is to be subtracted from A, the computer hardware forms the 2's complement of B and then adds it to A. Thus

$$S = A + B' = A + (-B) = A - B$$

Eqns. (2.1 and 2.2) represent algebraic addition and subtraction. A and B may represent either positive or negative numbers. Moreover, the final carry has no significance and is not used.

#### **Conversion of Binary to Decimal**

In the binary system, the weights of the binary bits after the binary point, can be written as

$$0.1011 = 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3} + 1 \times 2^{-4}$$

$= 1 \times^{1} + 0 \times^{1} + 1 \times^{1} + 1 \times^{1}$ 2 4 8 16

= 0.5 + 0 + 0.125 + 0.0625 = 0.6875 (decimal)

**Example** Express the number 0.6875 into binary equivalent Solution :

| Fraction | Fraction $\times 2$ | Remainder new fraction | Integer         |

|----------|---------------------|------------------------|-----------------|

| 0.6875   | 1.375               | 0.375                  | 1 (MSB)         |

| 0.375    | 0.75                | 0.75                   | 0               |

| 0.75     | 1.5                 | 0.5                    | 1               |

| 0.5      | 1                   | 0                      | 1(LSB) <b>\</b> |

The binary equivalent is 0.1011.

#### **OCTAL NUMEBR SYSTEM**

The number system with base (or radix) eight is known as the octal number system. In this system, eight symbols, 0, 1, 2, 3, 4, 5, 6 and 7 are used to represent numbers. Similar to decimal and binary number systems, it is also a positional system and has, in general, two parts: integer and fractional, set apart by a radix (octal) point  $(\cdot)$ . For example,  $(6327.4051)_8$  is an octal number. Using the weights it can be written as

$$(6327.4051)_8 = 6 \times 8^3 + 3 \times 8^2 + 2 \times 8^1 + 7 \times 8^0 + .4 \times 8^{-1}$$

$+ 0 \times 8^{-2} + 5 \times 8^{-3} + 1 \times 8^{-4}$ = 3072 + 192 + 16 + 7 +

$=(3287.5100098)_{10}$

Thus,  $(6327.4051)_8 = (3287.5100098)_{10}$

#### **HEXADECIMAL NUMBER SYSTEM**

Hexadecimal number system is very popular in computer uses. The base for hexadecimal number system is 16 which requires 16 distinct symbols to represent the numbers. These are numerals 0 through 9 and alphabets A through F. Since numeric digits and alphabets both are used to represent the digits in the hexadecimal number system, therefore, this is an alphanumeric number system. Table 2.3 gives hexadecimal numbers with their binary equivalents for decimal numbers 0 through 15. From the table, it is observed that there are 16 combinations of 4-bit binary numbers and sets of 4-bit binary numbers can be entered in the computer in the form of hexadecimal (hex.) digits. These numbers are required to be converted into binary representation, using hexadecimal-to-binary converter circuits before these can be processed by the digital circuits.

#### **Decimal-to-Hexadecimal Conversion**

The conversion from decimal to hexadecimal, the procedure used in binary as well as octal systems is applicable, using 16 as the dividing (for integer part) and multiplying (for fractional part) factor.

#### Hexadecimal-to-Binary Conversion

Hexadecimal numbers can be converted into equivalent binary numbers by replacing each hex digit by its equivalent 4-bit binary number.

Example Convert (2F9A)<sub>16</sub> to equivalent binary number.

Solution : Using Table 2.7, find the binary equivalent of each hex

digit.  $(2F9A)_{16} = (0010 \ 1111 \ 1001 \ 1010)_2$

$=(0010111110011010)_{2}$

#### **Binary-to-Hexadecimal Conversion**

Binary number can be converted into the equivalent hexadecimal numbers by making groups of four bits starting from LSB and moving towards MSB for integer part and then replacing each group of four bits by its hexadecimal representation.

For the fractional part, and above procedure is repeated starting from the bit next to the binary point and moving towards the right.

## CODES

Computers and other digital circuits process data in the binary format. Various binary codes are used to represent data which may be numeric, alphabets or special characters. Although, in every code used the information is represented in binary form, the interpretation of this binary information is possible only if the code in which this information is available is known. For example, the binary number 1000001 represents 65 (decimal) in straight binary, 41 (decimal) in BCD and alphabet A in ASCII code. A user must be very careful about the code being used while interpreting information available in the binary format. Codes are also used for error detection and error correction in digital systems.

#### **BINARY CODED DECIMAL (BCD)**

Computers work with binary numbers. We work with decimal numbers. A code is needed to represent decimal numbers and binary numbers. A weighted binary code is one in which each number carries a certain weight. A string of 4 bits is known as nibble. Binary code decimal (BCD) means that each decimal digit is represented by a nibble (binary code of 4 digits). Main BCD codes have been proposed, e.g., 8421, 2421, 5211, X53. Out of these 8421 code is the most predominant BCD code. The designation 8421 indicates the weights of the 4 bits (8, 4, 2 and 1 respectively starting from the left most bit). When one refers to a BCD code, it always means 8421 code. Though 16 numbers (2<sup>4</sup>) can be represented by 4 bits, only 10 of these are used. Table 2.4 shows the BCD code. The remaining 6 combinations, i.e., 1010, 1011, 1100, 1101, 1110 and 1111 are invalid in 8421 BCD code. To express any number in BCD code, each decimal number is replaced by the appropriate four bit code.

## **BCD ADDITION**

Addition is the most important arithmetic operation. Subtraction, multiplication and division can be done by using addition. The rules for BCD addition are :

- 1. Add the two numbers using binary addition (section 2.5). If the four bit sum is equal or less than 9(i.e., equal to or less than 1001) it is a valid BCD number.

- 2. If the four bit sum is more than 9 or a carry is generated from the group of 4 bits, the result is invalid. In such a case add 6(i.e., 0110) to the four bit sum to

skip the 6 invalid states. If a carry is generated when adding 6, add the carry to the next four bit group.

#### **GRAY CODE**

It is an unweighted code. The bit positions do not have any specific weights assigned to them. However, the most important characteristic of this code is that only a signal bit change occurs when going from one code number to next. (In binary systems all the 4 bits change when we go from 0111 to 1000. i.e.,  $7_{10}$  to  $8_{10}$ ). The single bit change property is important in some applications, e.g., shaft position encoders. In these applications the chances of error increase if more than one bit change occurs.

#### **Binary to Gray Conversion**

The rules for changing binary number into equivalent Gray code are :

1. The left most bit (most significant bit) in Gray code is the same as the left most bit in binary

> 0 1 1 Binary 1  $\downarrow$ 1

Grav

2. Add the left most bit to the adjacent bit

> 1 +0 1 1 1 1

Add the next adjacent pair 3.

> $1 \ 0 \ + \ 1$ 1 1 1 1 0

Add the next adjacent pair and discard carry 4.

> 1 0 1 + 1 1 1 1 0

Continue the above process till completion. 5.

## Gray to Binary Conversion

the method to convert from Gray code to binary is an under:

1. Left most bit in binary is the same as the left most bit in Gray

> code. 1 1 0 1 1 Gray

$\downarrow$

1 Binary 2. Add the binary MSB to the Gray digit in the adjacent position. Discard 0 1 carry 1 1 1 Gray 1  $\downarrow$ 0 1 Binary Add the binary digit generated in step 2 to the next Gray digit. Discard 3. carry 1 1 0 1 1 Gray 1  $\downarrow$

1 0 0 Binary

4. Continue the above process till all the digits are covered. Discard carry in each case

$\begin{array}{ccccccc} 1 & 1 & 0 \\ \downarrow & & & \end{array} \begin{array}{c} 1 & 1 & & \text{Gray} \\ 1 & 0 & 0 & 1 & 0 & & \text{Binar} \\ y \end{array}$

## 2.10.2 EXCESS 3 CODE

Excess 3 is a digital code obtained by adding 3 to each decimal digit and then converting the result to four bit binary. It is an unweighted code, i.e., no weights can be assigned to any of the four digit positions.

**Example** Convert the following decimal numbers to excess 3 code (a) 14 (b) 32 (c) 46 (d) 430.

Solution : In each case add 3 to each digit in decimal number and then convert into

|        | binary. (a   | ) 1          | 4      | (b)          | 3 2                            |

|--------|--------------|--------------|--------|--------------|--------------------------------|

| +3 + 3 |              |              | +3 + 3 |              |                                |

| 4 7    |              |              | 6 5    |              |                                |

|        | $\downarrow$ | $\downarrow$ |        | $\downarrow$ | $\downarrow$                   |

|        | 010          | 0 0111       |        | 0110         | 1010                           |

|        | (c) 4        | 6            | (d)    | 4            | 3 0                            |

|        | + 3          | +3           |        | + 3 +        | - 3 +3                         |

|        | 7            | 9            |        | 7            | 6 3                            |

|        | $\downarrow$ | $\downarrow$ |        | $\downarrow$ | $\downarrow \qquad \downarrow$ |

|        | 011          | 1 1001       |        | 0111         | 0110 001                       |

|        |              |              |        |              | 1                              |

#### **ERROR DETECTION CODES**

Every digit of a digital system must be correct. An error in any digit can cause a problem because the computer may recognize it as something else. The correct ASCII code for A is 1000001. An error in one bit (i.e., 1000011) would mean C. Many methods have been devised to detect such errors.

### **Digital logic families**

The design of a logic system starts with the statement of logic problems. This problem is then translated into a truth table and then into a logic equation. The logic equation yields the logical blocks and their interconnection so that we get the desired output for the given input conditions. From the logical block we realize an actual digital circuit. The basic building block in a digital system is logic gate logic circuits have evolved into families each of which has its own advantages and disadvantages. Generally a digital system is designed with circuits from one family only.

## **CLASSIFICATION OF LOGIC FAMILIES**

## **Classification as per Level of Integration**

As per this classification digital integrated circuits can be classified as small scale integration (SSI), Medium scale integration (MSI), large scale integration (LSI), Very large scale integration (VLSI) and ultra large scale integration (ULSI). This classification is given in SSI are the least complex and include basic gates and flip flops. They are available in dual in package (DIP) or flat package and 14 or 16 pin versions. Small digital sub systems form the MSI category. The complex logic functions, e.g., adders, registers, comparators, code converters, counter, multiplexers etc., are fabricated in MSI. They are also available in dual in package (KIP), flat package and carrier package with 24 or 28 pins.

#### **Classification as per Technology**

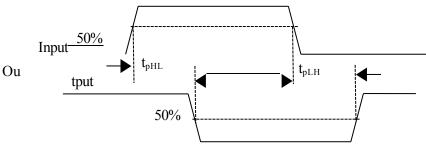

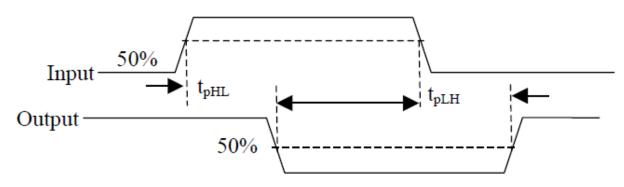

Digital ICS are manufactured by two technologies viz., Bipolar and MOS. The bipolar family uses transistor fabricated on a chip. This family includes DTL (Diode transistor logic using diodes and transistor), TTL (transistor-transistor logic which propagation delay time of the logic gate is taken as the average of these two delay times.

Input and output voltage waveforms to define propagation delay tines.

#### **Power Dissipation**

This is the amount of power dissipated in an IC. It is determined by the current,  $1_{CC}$ , that it draws from the V<sub>CC</sub> supply, and is given by V<sub>CC</sub> ×  $1_{CC}$ .  $1_{CC}$  is the average value of  $1_{CC}$  (0) and  $1_{CC}$  (1). This power is specified in milli watts.

## **Figure of Merit**

The figure of merit of a digital IC is defined as the product of speed and power. The speed is specified in terms of propagation delay time expressed in nanoseconds.

Figure of merit = propagation delay time (ns)  $\times$  power

(mW) It is specified in pico joules (ns  $\times$  mW = p<sup>J</sup>)

A low value of speed-power product is desirable. In a digital circuit, if it is desired to have high speed, i.e. low propagation delay, then there is a corresponding increase in the power dissipation and vice-versa.

#### Fan-Out

This is the number of similar gates which can be driven by a gate, High fan-out is advantageous because it reduces the need for additional drivers to drive more gates.

#### **Current and Voltage Parameters**

The following currents and voltages are specified which are very useful in the design of digital system.

**High-level input voltage**,  $V_{IH}$ : This is the minimum input voltage which is recognized by the gate as logic 1.

Low-level input voltage,  $V_{IL}$ : This is the maximum input voltage which is recognized

by the gate as logic 0.

TTL is the most popular family in SSI and MSI category. MOS family includes PMOS (pchannel MOSFET), NMOS (n0channel MOSFET) and CMOS (complementary MOSFET). PMOS is almost obsolete. NMOS is dominating the LSI field. CMOS is the most commonly used technology for digital wrist watches pocket calculators etc. The technologies being used now-a-days are TTL, ECL and CMOS. Before discussing these technologies we discuss the important specifications of digital ICs.

#### **CHARACTERISTICS OF DIGITAL ICs**

With the widespread use of ICs in digital systems and with the development of various Technologies for the fabrication of ICs, it has become necessary to be familiar with the

characteristics of IC logic families and their relative advantages and disadvantages. Digital ICs are classified either according to the complexity of the circuit, as the relative number of individual basic gates (2-input NAND gates) it would require to build the circuit to accomplish the same logic function or the number of components fabricated on the chip.

The various characteristics of digital ICs used to compare their performances are:

- 1. Speed of operation,

- 2. Power dissipation,

- 3. Figure of merit,

- 4. Fan-out,

- 5. Current and voltage parameters,

- 6. Noise immunity,

- 7. Operating temperature range,

- 8. Power supply requirements, and

- 9. Flexibilities available.

## **Speed of Operation**

The speed of a digital circuit is specified in terms of the propagation delay time. The input and output waveforms of a logic gate are shown. The delay times are measured between the 50 per cent voltage levels of input and output waveforms. There are two delay times: tpLH, when the output goes from the HIGH state to the LOW state and tpLH, corresponding to the output making a transition from the LOW state to the HIGH state. The propagation delay time of the logic gate is taken as the average of these two delay times.

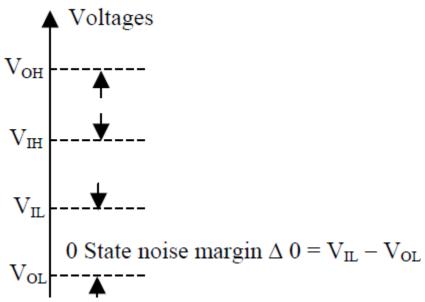

## **Noise Immunity**

The input and output voltage levels defined above are shown. Stray electric and magnetic fields may induce unwanted voltages, known as noise, on the connecting wires between logic circuits. This may cause the voltage at the input to a logic circuit to drop below VIH or rise above VIL and may produce undesired operation. The circuit's ability to tolerate noise signals is referred to as the no8ise immunity, a quantitative measure of which is called noise margin. Noise margins are illustrated in Fig. The noise margins defined above are referred to as dc noise margins. Strictly speaking, the noise is generally thought of as an a.c. signal with amplitude and pulse width.

## **Operating Temperature**

The temperature range in which an IC functions properly must be known. The accepted temperature ranges are: 0 to + 70  $^{0}$ C for consumer and industrial applications and --55  $^{0}$ C to + 125  $^{\circ}$ C for military purposes.

#### **Power Supply Requirements**

The supply voltage (s) and the amount of power required by an IC are important characteristics required to choose the proper power supply.

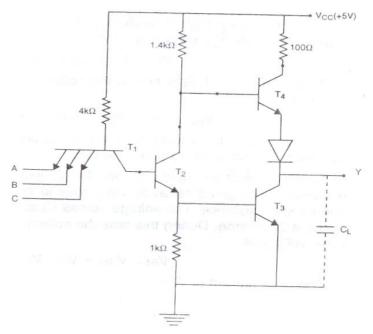

## **TRANSISTOR-TRANSISTOR LOGIC (TTL)**

Fig. below shows a TTL NAND gate with a totem pole output. The totem pole output means that transistor T4 sits atop T3 so as to give low output impedance. The low output impedance implies a short time constant RC so that the output can change quickly from one state to another. T1 is a multiple emitter transistor. This transistor can be thought of as a combination of many transistors with a common base and collector. Multiple emitter transistors with about 60 emitters have been developed. In the T1 has 3 emitters so that there can be three inputs A, B, C. The transistor T2 acts as a phase splitter because the emitter voltage is out of phase with the collector voltage. The transistors T3 and T4 form the totem pole output. The capacitance CL represents the stray capacitance etc. The diode D is added to ensure that T4 is cut off when output is low. The voltage drop of diode D keeps the base emitter junction of T4 reverse biased so that only T3 conducts when output is low. The operation can be summed up as under:

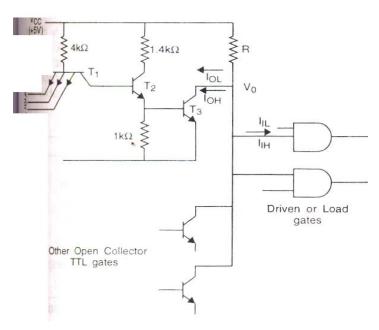

### **Open Collector Connection**

TTL gates without active pull up and with collector open and brought out can be connected for wired AND connection. Fig.below shows one such connection. In this case all the open collector terminals share one common pull up resistance R. The size of this resistance R depends on the number of open collector gates, required noise margin, fan out etc. In any of the input (say A) of TTL gate is not used (and left unconnected or open) the corresponding emitter base junction of T1 will not be forward biased and behave as if logical 1 is applied to this input. Therefore, the unused input terminal of any TTL gate should preferably be TTL gates are used with clamping diodes connected between each input terminal and ground as shown in Fig. These diodes clamp the input to -0.7 V and minimize undesired negative noise transients.

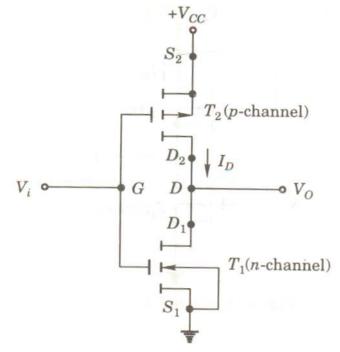

#### **CMOS LOGIC**

A complementary MOSFET (CMOS) is obtained by connecting a p-channel and an n-channel MOSFET is series, with drains tied together and the output is taken at the common drain. Input is applied at the common gate formed by connecting the two gates together. In a CMOS, p-channel and n-channel enhancement MOS devices are fabricated on the same chip, which makes its fabrication more complicated and reduces the packing density. But because of negligibly small power consumption, CMOS is ideally suited for battery operated systems. Its speed is limited by substrate capacitances. To reduce the effect of these substrate capacitances, the latest technology known as silicon on sapphire (SOS) is used in microprocessor fabrication which employs an insulating substrate (sapphire). CMOS is becoming very popular in MSI and LSI areas.

## **CMOS** Inverter

The basic CMOS logic circuit is an inverter shown in Fig. For this circuit the logic levels are 0 V (logic 0) and VCC (logic 1). When Vi = VCC, T1 turns On and T2 turns OFF. Therefore V0 = 0 V, and since the transistors are connected in series the current ID is very small. On the other hand, when Vi = 0 V, T1 turns OFF and T2 turns ON giving an output voltage V0 = VCC and ID is again very small. In either logic state, T1 or T2 is OFF and the quiescent power dissipation which is the product of the OFF leakage current and VCC is very low. More complex functions can be realized by combinations of inverters.

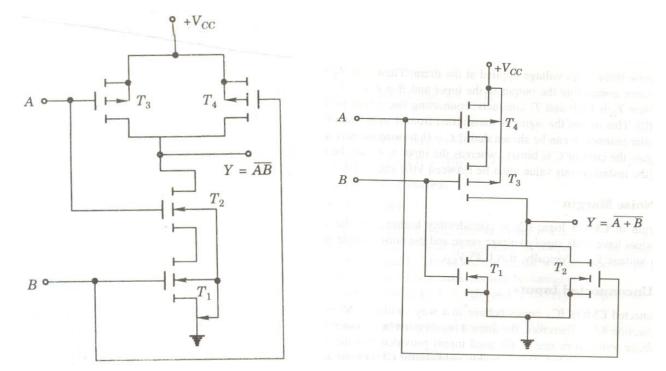

#### **CMOS NAND and NOR Gates**

A 2-input CMOS NAND and NOR gate shown in Fig. In the NAND gate, the NMOS drivers are connected in series, whereas the PMOS loads are connected in parallel. On the other hand, the CMOS NOR gate is obtained by connecting the NMOS drivers in parallel and PMOS loads in series. The operation of NAND gate can be understood from Table.

A 2-input CMOS NAND gate

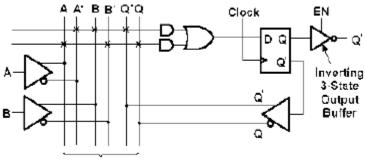

#### **TRI-STATE LOGIC**

In normal logic circuits there are two states of the output, LOW and HIGH. If the output is not in the LOW state, it is definitely in the other state (HIGH). Similarly, if the output is not in the HIGH state, it is definitely in the LOW state. In complex digital systems like microcomputers and microprocessors, a number of gate outputs may be required to be connected to a common line which is referred to as a bus which, in turn, may be required to drive a number of gate inputs. When a number of gate outputs are connected to the bus, we encounter some difficulties. These are:

1. Totem-pole outputs cannot be connected together because of very large current drain from the supply and consequent heating of the ICs which may get damaged.

2. Open-collector outputs can connected together with a common collector-resistor connected externally. This causes the problems of loading and speed of operation.

To overcome these difficulties, special circuits have been developed in which there is one more state of the output, referred to as the *third state* or *high-impedance state*, in addition to the LOW and HIGH states. These circuits are known as TRI-STATE, *tri-state logic* (TSL) or *three-state logic*. TRI-STATE, is a registered Trade Mark of National Semiconductor Corporation of USA.

There is a basic functional difference between wired-OR and the TSL. For the wired-OR connection of two functions Y1 and Y2 is

## Y = Y1 + Y2

Whereas for TSL, the result is not a Boolean function but an ability to multiplex many functions economically.

# **Module-II**

# **Combinational Digital Circuits**

Boolean algebraic theorems are used for the manipulations of logical expressions. It has also been demonstrated that a logical expression can be realized using the logic gates. The number of gates and the number of input terminals for the gates required for the realization of a logical expression, in general, get reduced considerably if the expression can be simplified. Therefore, the simplification of logical expression is very important as it saves the hardware required to design a specific system. A large number of functions are available in IC form and therefore, we should be able to make optimum use of these ICs in the design of digital systems. That is, our aim should be to minimize the number of IC packages. Basically, digital circuits are divided into two broad categories:

- 1. Combinational circuits, and

- 2. Sequential circuits,

In *combinational circuits*, the outputs at any instant of time depend upon the inputs present at that instant of time. This means there is no memory in these circuits. There are other types of circuits in which the outputs at any instant of time depend upon the present inputs as well as past inputs/outputs. This means that there are elements used to store past information. These elements are known as *memory*. Such circuits are known as *sequential circuits*. A sequential logic system may have combinational logic sub-systems. The design of combinational circuits will be discussed here. Sequential circuit design will be discussed later. The design requirements of combinational circuits may be specified in one of the following ways

- 1. A set of statements

- 2. Boolean expression, and

- 3. Truth table.

The aim is to design a circuit using the gates already discussed or some other circuits which are in fact derived from the basic gates. As is usual in any engineering design, the number of components used should be minimum to ensure low cost, saving in space, power requirements, etc. There can be two different approaches to the design of combinational circuits. One of these is the traditional method, wherein the given Boolean expression or the truth table is simplified by using standard methods and the simplified expression is realized using the gates. The other method normally does not require any simplification of the logical expression or truth table, instead the complex logic functions available in medium scale integrated circuits (MSI) or large scale integrated circuits (LSI) can be directly used. Combinational circuit design using the traditional design methods has been discussed below. The following methods can be used to simplify the Boolean function:

1. Algebraic method,

- 2. Karnaugh map technique,

- 3. Variable entered aping (VEM) technique, and

## STANDARD FORMS OF LOGIC FUNCTIONS

Design of logic circuits starts with preparation of word equation or truth table for the desired output (0 or 1) for the given input conditions. A logic circuit to implement the above equation/truth table is to be synthesized. The logic expression can be either a sum of products or product of sums.

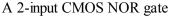

## Fundamental Products and Sum of Products

Fig. below shows four possible ways for connecting two input variables A, B and their complements A, B to AND gate. These four products AB, AB, AB and AB are known as fundamental products and are listed in Table

For three variables

| А | В | С | Fundamental products                   |

|---|---|---|----------------------------------------|

| 0 | 0 | 0 | $\overline{A}\overline{B}\overline{C}$ |

| 0 | 0 | 1 | $\overline{A}\overline{B}C$            |

| 0 | 1 | 0 | $\overline{A}B\overline{C}$            |

| 0 | 1 | 1 | ABC                                    |

| 1 | 0 | 0 | $A\overline{B}\overline{C}$            |

| 1 | 0 | 1 | $A\overline{B}C$                       |

| 1 | 1 | 0 | $AB\overline{C}$                       |

| 1 | 1 | 1 | ABC                                    |

#### Sum of Product in terms of Minterms

Since the terms ABC must appear in every product, a short hand notation has been developed to save the labour in writing down the letters again and again. TO use this notation substitute 0 for a letter with bar (i.e., NOT ed letter) and 1 for a letter without a br. Express the resultant binary number by a decimal number and write it as a subscript of m. This subscript is used in all truth tables and maps.

#### **Product of Sums**

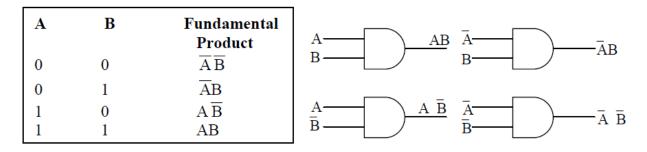

The product of sums, as the name suggests, is an expression involving the product of two or more terms where each term contains sum of a number of variables. The product of sum form is a dual of sum of product form. It may also contain a single variable term. The expression A(A + B) (C + D) is an example of product of sum form. Fig shows a logic circuit corresponding to expression A(A + B) (C + D).

Example Identify the form of the expression

Y = A(A + B) (C + D) (E + F)

Draw logic circuit.

Solution: It is product of sum form. Fig below shows the logic circuit. It has three OR gates and one AND gate.

#### Product of Sums in terms of Max Terms

Just as the sum of products can be written in short hand using minterms, the product of sums can be written in short hand using max terms. If a system has variables A, B, C then the max terms would be in the form A + B + C. A Boolean expression written in max terms takes the form

$$Y = \prod M(0, 1, 3, 4)$$

Where the capital  $\Pi$  represents the product and M stands for max terms.

The numbering of max terms is different from numbering of min terms. The unbarred letters represent 0s and the barred (NOT ed) letters represent 1s in forming the maxterms designation.

## SIMPLIFICATION OF LOGICAL FUNCTIONS USING K-MAP

Simplification of logical functions with K-map is based on the principle of combining terms in adjacent cells. Two cells are said to be adjacent if they differ in only one variable. For example, in the two-variable K-maps, the top two cells are adjacent and the bottom two cells are adjacent. Also, the left two cells and the right two cells are adjacent. It can be verified that in adjacent cells one of the literals in same, whereas the other literal appears in uncomplemented form in one and in the complemented form in the other cell. Similarly, we observe adjacent cells in the 3-variable and 4-variable K-maps

## Grouping Two Adjacent Ones

If there are two adjacent ones on the map, these can be grouped together and the resulting term will have one less literal than the original two terms. It can be verified for each of the groupings of two ones as given in Table

| Cell with | Decimal numbers of adjacent cell |            |               |

|-----------|----------------------------------|------------|---------------|

| decima1   | 2-variable                       | 3-variable | 4-variable    |

| number    |                                  |            |               |

| 0         | 1, 2                             | 1, 2, 4    | 1, 2, 4, 8    |

| 1         | 0, 3                             | 0, 3, 5    | 0, 3, 5, 9    |

| 2         | 0, 3                             | 0, 3, 6    | 0, 3, 6, 10   |

| 3         | 1, 2                             | 1, 2, 7    | 1, 2, 7, 11   |

| 4         |                                  | 0, 5, 6    | 0, 5, 6, 12   |

| 5         |                                  | 1, 4, 7    | 1, 4, 7, 13   |

| 6         |                                  | 2, 4, 7    | 2, 4, 7, 14   |

| 7         |                                  | 3, 5, 6    | 3, 5, 6, 15   |

| 8         |                                  |            | 0, 9, 10, 12  |

| 9         |                                  |            | 1, 8, 11, 13  |

| 10        |                                  |            | 2, 8, 11, 14  |

| 11        |                                  |            | 3, 9, 10, 15  |

| 12        |                                  |            | 4, 8, 13, 14  |

| 13        |                                  |            | 5, 9, 12, 15  |

| 14        |                                  |            | 6, 10, 12, 15 |

| 15        |                                  |            | 7, 11, 13, 14 |

#### Grouping Four Adjacent Ones

Four cells form a group of four adjacent ones if two of the literals associated with the minterms/maxterms are not same and the other literals are same. Table below gives all possible groups of four adjacent ones for each cell in a 3-variable map. In case of 2-variable map, there is only one possibility corresponding to entry 1 in all the four cells, and the simplified expression will be Y=1. That is, Y always equals 1(independent of the variables). On the basis of groupings of 4 adjacent ones given in Table 3.5, we can find the groupings in K-maps of four or more variables. In the case of a four-variable Kmap, there are six possible groupings of 4-variables involving any cell. It is left to the reader to verify this fact.

| Cell with decimal | Decimal numbers of cells forming |               |  |

|-------------------|----------------------------------|---------------|--|

| number            | groups of adjacent fours         |               |  |

| 0                 | (0, 2, 6, 4), (0, 1, 2, 3),      | (0, 1, 4, 5), |  |

| 1                 | (1, 0, 2, 3), (1, 3, 7, 5),      | (1, 0, 4, 5), |  |

| 2                 | (2, 0, 6, 4), (2, 3, 1, 0),      | (2, 3, 6, 7), |  |

| 3                 | (3, 1, 7, 5), (3, 2, 1, 0),      | (3, 2, 6, 7), |  |

| 4                 | (4, 6, 2, 0), (4, 5, 6, 7),      | (4, 5, 0, 1), |  |

| 5                 | (5, 1, 3, 7), (5, 4, 6, 7),      | (5, 4, 0, 1), |  |

| 6                 | (6, 0, 2, 4), (6, 7, 4, 5),      | (6, 7, 2, 3), |  |

| 7                 | (7, 1, 3, 4), (7, 6, 4, 5),      | (7, 6, 2, 3), |  |

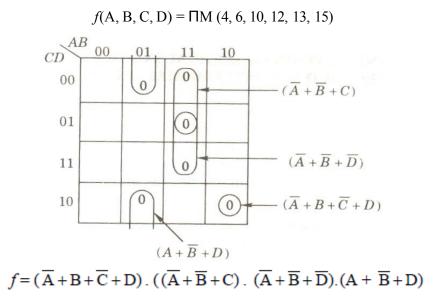

Example 3.16 Minimize the logic function of  $f(A, B, C, D) = \prod M (4, 6, 10, 12, 13, 15)$  in POS form.

Solution :

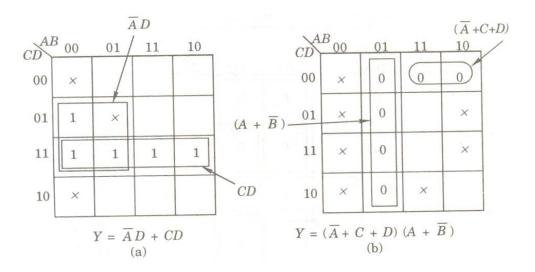

#### **DON'T-CARE CONDITIONS**

We enter 1's and 0's in the map corresponding to input variables that make the function equal to 1 to 0, respectively. The maps are simplified using either 1's or 0's. Therefore, we make the entries in the map for either 1's or 0's. The cells which do not contain 1 are assumed to contain 0 and vice-versa. This is not always true since there are cases in which certain combinations of input variables do not occur. Also, for some functions the outputs corresponding to certain combinations of input variables do not matter. In such situations the designer has flexibility and it is left to him whether to assume a 0 or 1 as output for each of these combinations. This

condition is known as *don't-care* condition and can be represented on the K-map as a × mark in

the corresponding cell. The  $\times$  mark in a cell may be assumed to be a 1 or a 0 depending upon which one leads to a simpler expression. The function can be specified in one of the following ways:

1. In terms of minterms and don't-care conditions, For example,

$f(A, B, C, D) = \Sigma m (1, 3, 7, 11, 15) + d(0, 2, 5)$

Its K-map and the minimized expression are given in Fig. 2. In terms of maxterms and don't-care conditions. For example,

$f(A, B, C, D) = \prod (4, 5, 6, 7, 8, 12) \cdot d(1, 2, 3, 9, 11, 14)$

Its K-map and the minimized expression are given in Fig.

3. In terms of truth table. For example, consider the truth table.

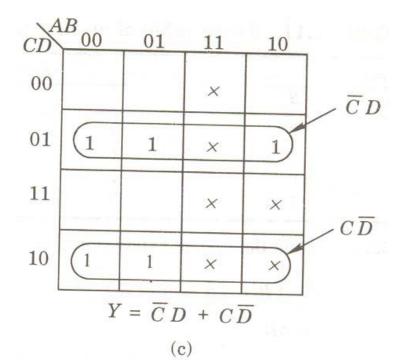

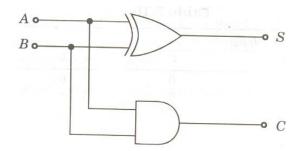

## **Arithmetic Circuits**

**1. Half-adder**. A logic circuit for the addition of two one-bit numbers is referred to as an half-adder. The addition process is illustrated in Section 2.5 and is reproduced in truth table. Here, A and B are the two inputs and S (SUM) and C(CARRY) are the two outputs.

| Inputs |   | Outputs |   |  |

|--------|---|---------|---|--|

| А      | В | S       | С |  |

| 0      | 0 | 0       | 0 |  |

| 0      | 1 | 1       | 0 |  |

| 1      | 0 | 1       | 0 |  |

| 1      | 1 | 0       | 1 |  |

$S = \overline{A}B + A\overline{B} = A \oplus B$

## C = AB

The realization of an half-adder using gates is shown in Fig.

## Full-adder

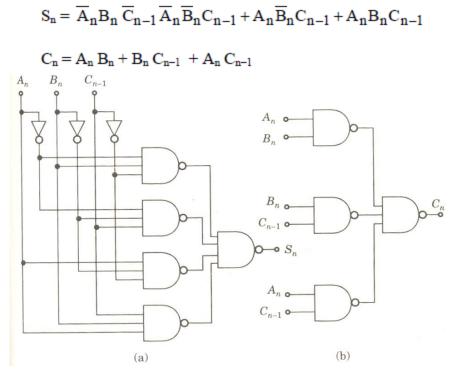

An half-adder has only two inputs and there is no provision to add a carry coming from the lower order bits when multi bit addition is performed. For this purpose, a third input terminal is added and this circuit is used to add An, Bn, and Cn-1, where An and Bn are the nth order bits of the numbers A and B respectively and Cn-1 is the carry generated from the addition of (n-1)th order bits. This circuit is referred to as *full-adder* and its truth table is given in Table

| Inputs         |                                 |   | Outputs |                |  |

|----------------|---------------------------------|---|---------|----------------|--|

| A <sub>n</sub> | B <sub>n</sub> C <sub>n-1</sub> |   | Sn      | C <sub>n</sub> |  |

| 0              | 0                               | 0 | 0       | 0              |  |

| 0              | 0                               | 1 | 1       | 0              |  |

| 0              | 1                               | 0 | 1       | 0              |  |

| 0              | 1                               | 1 | 0       | 1              |  |

| 1              | 0                               | 0 | 1       | 0              |  |

| 1              | 0                               | 1 | 0       | 1              |  |

| 1              | 1                               | 0 | 0       | 1              |  |

| 1              | 1                               | 1 | 1       | 1              |  |

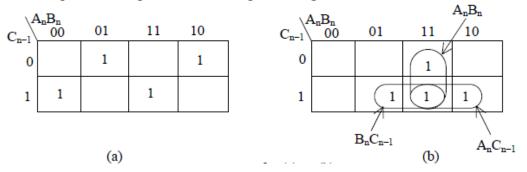

The K-maps for the outputs  $S_n$  and  $C_n$  are given in Fig. 3.29.

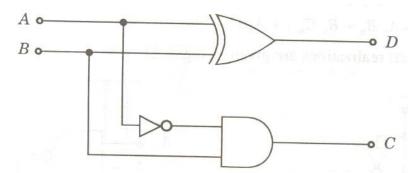

#### Half-sub-tractor.

A logic circuit for the subtraction of B (subtrahend) from A (minuend) where A and B are 1-bit numbers is referred to as a *half-sub-tractor*. The subtraction process is reproduced in truth table form in Table 3.13. Here, A and B are the two inputs and D(difference) and C (borrow) are the two outputs.

| Inputs |   | Outputs |   |  |

|--------|---|---------|---|--|

| A      | В | D       | С |  |

| 0      | 0 | 0       | 0 |  |

| 0      | 1 | 1       | 1 |  |

| 1      | 0 | 1       | 0 |  |

| 1      | 1 | 0       | 0 |  |

$D = \overline{A}B + A\overline{B} = A \oplus B$

$$C = \overline{A}B$$

The realization of a half-subtractor using gates is shown in Fig.

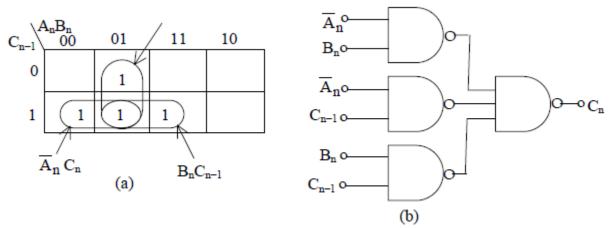

**Full-subtractor.** Just like a full-adder, we require a *full-subtractor* circuit for performing multibit subtraction wherein a borrow from the previous bit position may also be there. A full subtractor will have three inputs, An (minuend), Bn (sub-trahend) and Cn-1 (borrow from the previous stage) and two outputs, Dn (difference) and Cn (borrow). Its truth table is given in Table. The K-map for the output Dn is exactly same as the K-map for Sn of the adder circuit and therefore, its realization is same as given in Fig.

|       | Inputs                    | Outputs          |    |                |

|-------|---------------------------|------------------|----|----------------|

| $A_n$ | $\mathbf{B}_{\mathbf{n}}$ | C <sub>n-1</sub> | Sn | C <sub>n</sub> |

| 0     | 0                         | 0                | 0  | 0              |

| 0     | 0                         | 1                | 1  | 1              |

| 0     | 1                         | 0                | 1  | 1              |

| 0     | 1                         | 1                | 0  | 1              |

| 1     | 0                         | 0                | 1  | 0              |

| 1     | 0                         | 1                | 0  | 0              |

| 1     | 1                         | 0                | 0  | 0              |

| 1     | 1                         | 1                | 1  | 1              |

$C_n = \overline{A}_n B_n + \overline{A}_n C_{n-1} + B_n C_{n-1}$

#### **BCD-to-7-Segment Decoder**

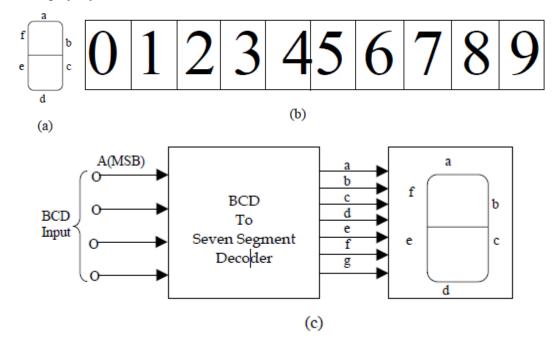

A digital display that consists of seven LED segments is commonly used to display decimal numerals in digital systems. Most familiar examples are electronic calculators and watches where one 7-segment display device is used for displaying one numeral 0 through 9. For using this display device, the data has to be converted from some binary code to the code required for the display. Usually, the binary code used is natural BCD. Figure (a) shows the display device, Fig.(b) shows the segments which must be illuminated for each of the numerals and Fig.(c) gives the display system.

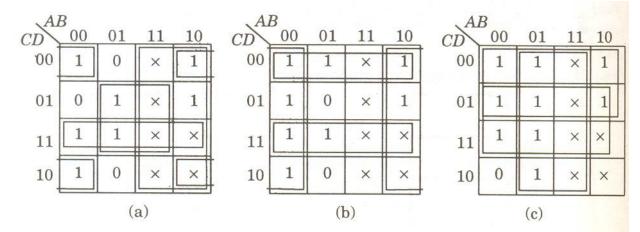

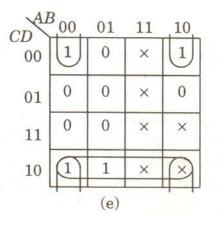

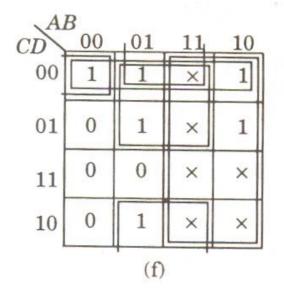

Table below gives the truth table of BCD-to-7-segment decoder. Here ABCD is the natural BCD code for numerals 0 through 9. The entries in the K-map corresponding to six binary combinations not used in the truth table are x - don't-care. The K-maps are simplified and the minimum expressions are given by:

$$a = \overline{B}\overline{D} + BD + CD + A$$

$$b = \overline{B} + \overline{C}\overline{D} + CD$$

$$c = B + \overline{C} + D = \overline{B}\overline{C}\overline{D}$$

$$d = \overline{B}\overline{D} + C\overline{D} + \overline{B}C + B\overline{C}D$$

$$e = \overline{B}\overline{D} + C\overline{D}$$

$$f = A + \overline{C}\overline{D} + B\overline{C} + B\overline{D}$$

$$g = A + B\overline{C} + \overline{B}C + C\overline{D}$$

| Decimal            |   | Inp | out |   |   |   |   | Outputs |   |   |   |

|--------------------|---|-----|-----|---|---|---|---|---------|---|---|---|

| digit<br>displayed | A | В   | С   | D | a | b | с | d       | e | f | g |

| 0                  | 0 | 0   | 0   | 0 | 1 | 1 | 1 | 1       | 1 | 1 | 0 |

| 1                  | 0 | 0   | 0   | 1 | 0 | 1 | 1 | 0       | 0 | 0 | 0 |

| 2                  | 0 | 0   | 1   | 0 | 1 | 1 | 0 | 1       | 1 | 0 | 1 |

| 3                  | 0 | 0   | 1   | 1 | 1 | 1 | 1 | 1       | 0 | 0 | 1 |

| 4                  | 0 | 1   | 0   | 0 | 0 | 1 | 1 | 0       | 0 | 1 | 1 |

| 5                  | 0 | 1   | 0   | 1 | 1 | 0 | 1 | 1       | 0 | 1 | 1 |

| 6                  | 0 | 1   | 1   | 0 | 0 | 0 | 1 | 1       | 1 | 1 | 1 |

| 7                  | 0 | 1   | 1   | 1 | 1 | 1 | 1 | 0       | 0 | 0 | 0 |

| 8                  | 1 | 0   | 0   | 0 | 1 | 1 | 1 | 1       | 1 | 1 | 1 |

| 9                  | 1 | 0   | 0   | 1 | 1 | 1 | 1 | 0       | 0 | 1 | 1 |

Truth table of BCD-to-7 segment decoder

| CD | 300 | 01  | 11 | 10 |

|----|-----|-----|----|----|

| 00 | 1   | 0   | ×  | 1  |

| 01 | 0   | 1   | ×  | 0  |

| 11 | 1   | 0   | ×  | ×  |

| 10 | 1   | 1   | ×  | ×  |

|    |     | (d) | )  |    |

#### **BCD ADDER**

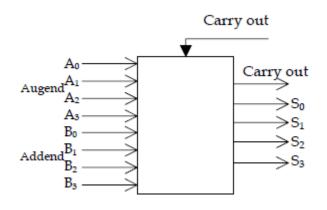

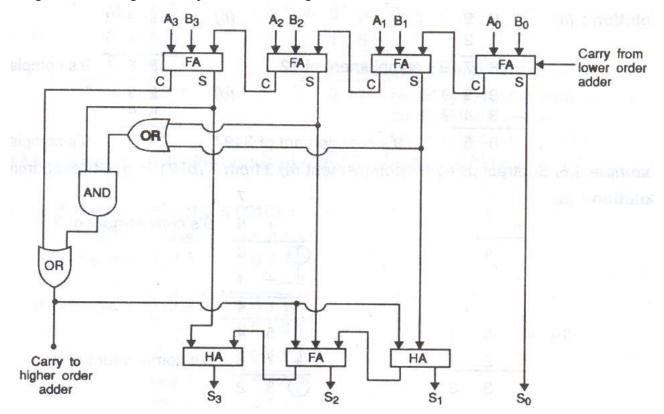

We have discussed the BCD number representation earlier. In BCD system each decimal digit is represented by its equivalent 4 bit binary number, e.g., 63 is written as 01100011 where 0110 represents 6 and 0011 represents 3. Since the highest decimal number is 9 (i.e., 1001) the binary combinations 1010, 1011, 1100, 1101, 1110 and 1111 are not valid in BCD system. In BCD addition, as and when the sum exceeds 9, we add 6 to the sum. A block diagram of BCD adder has been shown in Fig.. It has 9 bits of inputs. 4 bits of augend, 4 bits of addend and one bit for carry in from the lower stage. The output has 5 bits, i.e., 4 bits of SUM and one bit for carry out. Fig below shows the logic diagram of BCD adder made up from full and half adders,

OR gates and AND gate. It has provision for taking care of invalid combinations in BCD

```

BCD adder

6 + 7 = 13 \text{ or } 0110 + 0111 = 1101

+ 0110

1 0011 = 3

\downarrow

Carry

8 + 6 = 14 \text{ or } 1000 + 0110 = 1110

+ 0110

1 0011 = 3

\downarrow

Carry

Carry

```

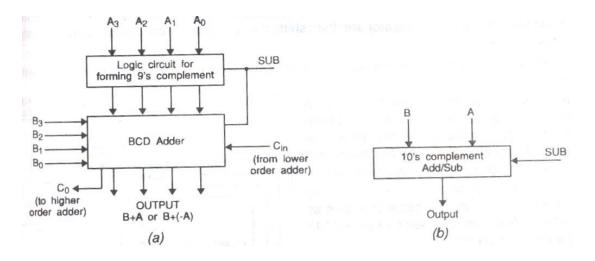

## **BCD ADDER/SUBTRACTOR**

BCD addition and subtraction is very easy is 10's complement and is used in calculators. The logic circuits of Fig.(a) and (b) are connected in tandem. A block diagram of BCD adder/subtractor is shown in Fig. 3.39 (a). Let B3 B2 B1 B0 be the first BCD number and let A3 A2 A1 A0 be the number to be added or subtracted from the first number. The number B3 B2 B1 B0 is fed directly to the BCD adder/subtractor while

BCD adder/subtractor (a) block diagram (b) symbol

When SUB is low, the A bits pass through the logic circuit as it is and BCD adder gives the sum.\* S = A + B When SUB is high, A bits are converted to 9's complement by the logic circuit. Moreover, a High SUB adds 0001 to the output of the logic circuit. This is equivalent to forming 10's complement of A bits. Thus we get the result as -A + B or B + (-A), i.e., number A is subtracted from number B. A symbol for BCD adder/subtractor is shown in Fig(b).

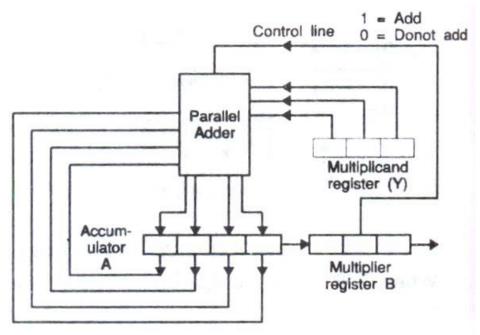

#### **BINARY MULTIPLIER**

We have discussed the rules for binary multiplication in chapter 2. These are  $0 \times 0 = 0$ ,  $0 \times 1 = 0$ ,  $1 \times 0 = 0$  and  $1 \times 1 = 1$ . To understand the working of a binary multiplier, let us multiply binary number 111 by 101. The method proceeds as under

|   |   | 1 | 1 | 1 | Multiplicand                             |

|---|---|---|---|---|------------------------------------------|

|   |   | 1 | 0 | 1 | Multiplier                               |

|   |   | 1 | 1 | 1 | First partial product                    |

|   | Q | 0 | 0 |   | Second partial product                   |

|   | 0 | 1 | 1 | 1 | Sum of first and second partial products |

| 1 | 1 | 1 |   |   | Third partial product                    |

| 0 | 0 | 0 | 1 | 1 | Final result                             |

From the above multiplication we can write the following rules for binary multiplication. The logic circuit for binary multiplier must follow these rules.

1. The partial product is 000, if the multiplier bit is 0 and is equal to multiplicand if multiplier bit is 1.

2. The product register\* needs twice as many bits as the multiplicand register.

3. The first partial product is shifted one place to the right (relative to second partial product) when adding.

From the above rules and procedure it is evident that logic circuit for binary multiplication does the following.

1. It stores the multiplicand and multiplier in separate registers say Y and B respectively.

2. It recognizes a bit as 0 or 1.

1

3. It stores partial products in accumulator (i.e., B).

4. If the right most bit in multiplier register is 0, it shifts the combined accumulator and B register right one place. If the right most bit in the B register is 1, it adds the contents of Y register (i.e., multiplicand) to the accumulator and then shifts the contents of accumulator and B register right by one place.

5. After each step it examines the right most bit in multiplier register (i.e., B register) whether the bit is 0 or 1.

6. In addition to above it examines the sign bits of multiplicand and multiplier. If both are the same, it stores the sign bit of final result as positive. If the two are different, it stores the sign bit of final result as negative.

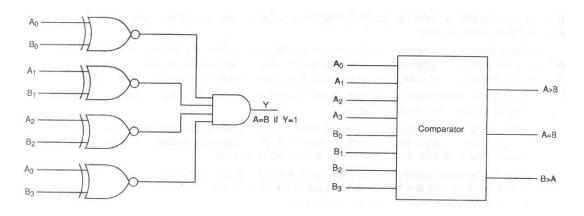

#### **MAGNITUDE COMPARATOR**

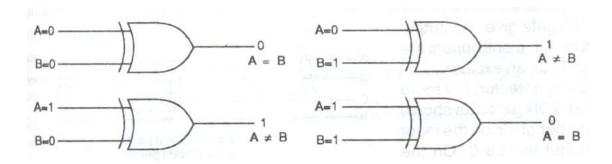

The function of a magnitude comparator is to compare the magnitudes of two numbers and indicate which one is bigger of the two. The simplest form of a magnitude comparator indicates whether the two numbers are equal or not. An exclusive OR is a comparator. If the two input bits are equal its output is 0, if not the output is 1. Thus a 1 bit comparator is just an exclusive OR gate as shown in Fig. below.

#### One bit magnitude comparator

When he numbers to be compared are of two bits we need the circuit of Fig.below.

LSBs of the two numbers are A0 and B0 and are fed to XOR gate 1. The MSB of the numbers are A1 and B1 and are fed to XOR gate 2. If the two numbers are equal, outputs of both XOR gates are 0 each and the outputs of NOT gates are 1 each. Then the output of AND gate is 1.

Thus a High output of AND gate indicates A = B. If  $A \neq B$ , one of the XOR gates gives High output and the final output of And gate is low. The above process can be expanded for numbers with more bits. Fig shows a magnitude comparator for 4 bit numbers. It is seen that the combination of XOR and NOT gate in Fig. 3.42 is an exclusive NOR gate. Therefore, the circuit of (a) shows Magnitude comparator for two bit numbers  $A_1 A_0$  and  $B_1 B_0$  exclusive NOR gates. As in the case of two bit numbers, a High output of AND gate indicates that A = B.

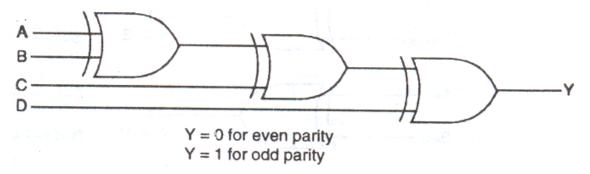

## **PARITY DETECTOR**

An exclusive OR gate gives an output of 1 if either of its inputs is 1. If both inputs are 0 or 1, the output is 0. Thus an exclusive OR gate can work as a parity detector. For more bits we use cascaded XOR gates as shown in Fig. below. If the number of 1's on the input is even, the final output will be 0. On the other hand if the number of 1's on the input is odd, the final output will be 1.

A parity bit can be added to the code group either at the beginning or at the end depending on the system design. However, the total number of 1's, including parity bit is even for even parity and odd for odd parity. Table below lists the parity bits for various numbers on BCD code.

|   | Even | Parity |   | Odd Parity |   |   |   |   |   |

|---|------|--------|---|------------|---|---|---|---|---|

| Р | 8    | 4      | 2 | 1          | Р | 8 | 4 | 2 | 1 |

| 0 | 0    | 0      | 0 | 0          | 0 | 0 | 0 | 0 | 0 |

| 1 | 0    | 0      | 0 | 1          | 0 | 0 | 0 | 0 | 1 |

| 1 | 0    | 0      | 1 | 0          | 0 | 0 | 0 | 1 | 0 |

| 0 | 0    | 0      | 1 | 1          | 1 | 0 | 0 | 1 | 1 |

| 1 | 0    | 1      | 0 | 0          | 0 | 0 | 1 | 0 | 0 |

| 0 | 0    | 1      | 0 | 1          | 1 | 0 | 1 | 0 | 1 |

| 0 | 0    | 1      | 1 | 0          | 1 | 0 | 1 | 1 | 0 |

| 1 | 0    | 1      | 1 | 1          | 0 | 0 | 1 | 1 | 1 |

| 1 | 1    | 0      | 0 | 0          | 0 | 1 | 0 | 0 | 0 |

| 0 | 1    | 0      | 0 | 1          | 1 | 1 | 0 | 0 | 1 |

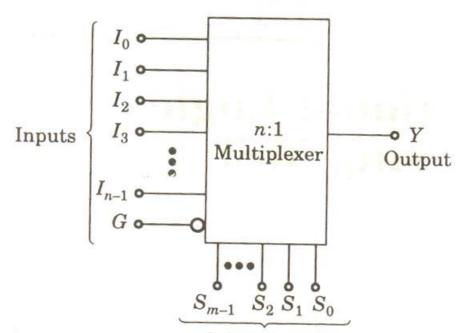

# Multiplexer

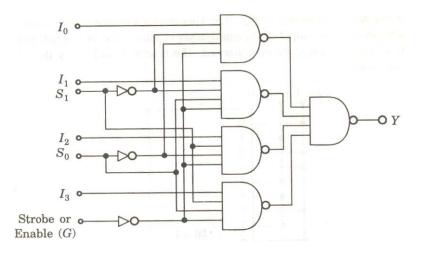

The multiplexer is a special combinational circuit that is one of the most widely used standard circuits in digital design. The multiplexer (or data selector) is a logic circuit that gates one out of several inputs to a single output. The input selected is controlled by a set of select inputs. Figure shows the block diagram of a multiplexer with n input lines and one output line. For selecting one out of n inputs for connection to the output, a set of m select inputs is required, where 2m = n. Depending upon the digital code applied at the select inputs one out of n data sources is selected and transmitted to a single output channel. Normally, a strobe (or enable) input (G) is incorporated which helps in cascading and it is generally active-low, which means it performs its intended operation when it is LOW.

Select inputs

| S              | Select inputs  |                |  |  |  |  |

|----------------|----------------|----------------|--|--|--|--|

| S <sub>1</sub> | S <sub>0</sub> | Y              |  |  |  |  |

| 0              | 0              | I <sub>0</sub> |  |  |  |  |

| 0              | 1              | $I_1$          |  |  |  |  |

| 1              | 0              | $I_2$          |  |  |  |  |

| 1              | 1              | $I_3$          |  |  |  |  |

$\mathbf{Y} = \ \overline{\mathbf{S}}_1 \ \overline{\mathbf{S}}_0 \ \mathbf{I}_0 + \ \overline{\mathbf{S}}_1 \ \mathbf{S}_0 \ \mathbf{I}_1 + \mathbf{S}_1 \ \overline{\mathbf{S}}_0 \ \mathbf{I}_2 + \mathbf{S}_1 \ \mathbf{S}_0 \ \mathbf{I}_3$

# **Combinational Logic Design Using Multiplexers**

The multiplexing function discussed above can conveniently be used as a logic element in the design of combinational circuits. Standard ICs are available for 2:1, 4:1, 8:1, and 16:1 multiplexers.

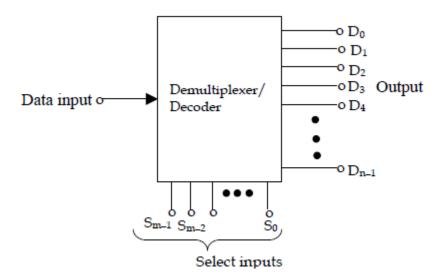

#### Demultiplexer

The demultiplexer performs the reverse operation of a multiplexer. It accepts a single input and distributes it over several outputs. Figure below gives the block diagram of a demultiplexer. The select input code determines to which output the data input will be transmitted.

The number of output lines in n and the number of select lines is m, where n = 2m. This circuit can also be used as binary-to-decimal decoder with binary inputs applied at the select input lines and the output will be obtained on the corresponding line. The data input line is to be connected to logic 1 level. This circuit can be designed using gates and it is left as an exercise for the reader. However, this device is available as an MSI IC and can conveniently be used for the design of combinational circuits. The device is very useful if multiple-output combinational circuit is to be designed, because this needs minimum package count. These devices are available as 2-line-to-line, 3-line-to-8-line, and 4-lineto- 16-line decoders.

# **ENCODERS**

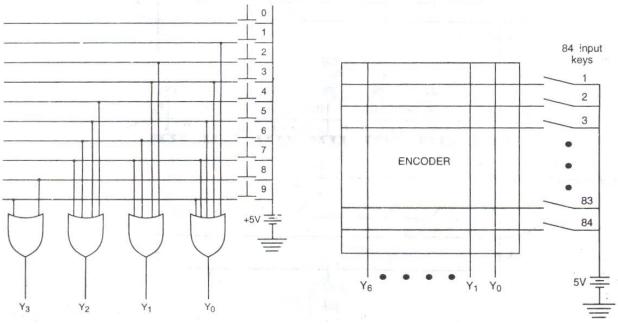

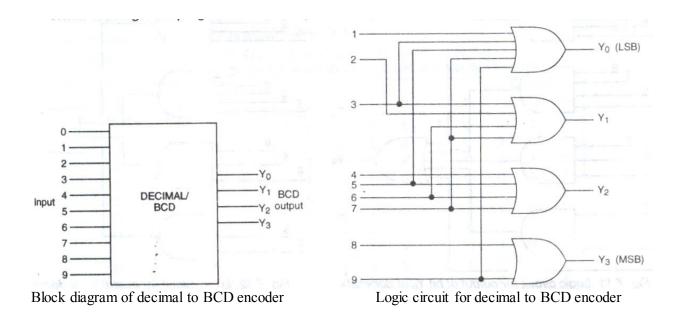

#### **Decimal to Binary Encoder**

Digital computers operate on binary system. However, we work on decimal numbers and alphabets. The decimal numbers and alphabets are known s alphanumeric characters. An encoder is a device which converts alphanumeric characters to binary codes. An encoder may be decimal to binary, hexadecimal to binary, octal to BCD etc. Fig. shows a decimal to binary encoder. When push button 0 is pressed, none of the OR gates is energized and all outputs are low so that the output word is Y3 Y2 Y1 Y0 = 0000

If push button 4 is pressed, Y2 OR gate has high input and the output word is Y3 Y2 Y1 Y0 =  $0 \ 1 \ 0 \ 0$

When switch 7 is pressed, OR gates Y2, Y1 and Y0 have high inputs and the output word is Y3 Y2 Y1 Y0 = 0 1 1 1

In a computer, it is required that a binary code be transmitted for every stroke of alphanumeric keyboard (a type writer or teletype). The keyboard of a computer has 26 capital alphabets, 26 lower case alphabets, 10 numerals (0 to 9) and about 22 special characters (+, – etc.). Thus, the total number of input codes is about 84. Encoder for generating an output binary word for these 84 inputs requires 7 bits (because 27 = 128 and 26 = 64). The block diagram of such an encoder is shown in Fig.(b). Whenever a key is pressed, the + 5 V supply is connected to one of the 84 input lines. Inside the box is an array of wires interconnected to generate the required code.

Fig. (a)Decimal to binary encoder

Fig.(b)Block diagram of decimal

| Decimal digit | BCD code       |                |       |                |  |  |  |

|---------------|----------------|----------------|-------|----------------|--|--|--|

|               | Y <sub>3</sub> | $\mathbf{Y}_2$ | $Y_1$ | Y <sub>0</sub> |  |  |  |

| 0             | 0              | 0              | 0     | 0              |  |  |  |

| 1             | 0              | 0              | 0     | 1              |  |  |  |

| 2             | 0              | 0              | 1     | 0              |  |  |  |

| 3             | 0              | 0              | 1     | 1              |  |  |  |

| 4             | 0              | 1              | 0     | 0              |  |  |  |

From Table, we can find the relationship between decimal digit and BCD bit. MSB of BCD bit is Y<sub>3</sub>. For decimal digits 8 or 9, Y<sub>3</sub>=1. Thus we can write OR expression for Y<sub>3</sub> bit as Y<sub>3</sub>=8+9 Bit Y<sub>2</sub> is 1 for decimal digits 4, 5, 6, and 7. Thus we can write OR expression Y<sub>2</sub>=4+5+6+7 Similarly, Y<sub>1</sub>=2+3+6+7 Y<sub>0</sub>=1+3+5+7+9

# **Priority Encoder**

When feeding data/program into a computer it is opposite that more than one key is pressed simultaneously. A priority function means the encoder will give priority to the

# Decoder

Let the input be 1101. We need an AND gate as the basic decoding element because an AND gate gives high output only when all its inputs are high. In addition we need a NOT gate to convert 0 in the 2s bit position to 1. Thus the circuit will have one AND gate and one NOT gate as shown in Fig.(a).

#### **Binary to Decimal Decoder**

Fig shows a binary to decimal decoder. The input is from a 4 bit register. The inputs would be of the form 0101, 1001 etc. A particular input would cause one of the 10 output lines to be energized so that the corresponding decimal number would be the output, if the input is 0101, only the Y5 AND gate has all high inputs and all other gates have at least one low input so that only Y5 gate would give an output and number 5 would be displayed. If the input is 0 1 1 1, only AND gate Y7 has all high input (all other AND gates have at least one low input) and number 7 is the output. The Boolean equations for different Y outputs are as under

| $Y_0 = \overline{A} \ \overline{B} \ \overline{C} \ \overline{D}$                                   |

|-----------------------------------------------------------------------------------------------------|

| $Y_1 = \overline{A} \ \overline{B} \ \overline{C} \ D$                                              |

| $\mathbf{Y}_2 = \overline{\mathbf{A}} \ \overline{\mathbf{B}} \ \mathbf{C} \ \overline{\mathbf{D}}$ |

| $Y_3 = \overline{A} \overline{B} C D$                                                               |

| $\mathbf{Y}_4 = \overline{\mathbf{A}} \ \mathbf{B} \ \overline{\mathbf{C}} \ \overline{\mathbf{D}}$ |

| $Y_5 = \overline{A} \ B \ \overline{C} \ D$                                                         |

| $Y_6 = \overline{A} B C \overline{D}$                                                               |

| $Y_7 = \overline{A} B C D$                                                                          |

| $Y_8 = A \overline{B} \overline{C} \overline{D}$                                                    |

| $Y_9 = A \overline{B} \overline{C} D$                                                               |

# **Procedure of Quine-McCluskey Tabular Method**

Follow these steps for simplifying Boolean functions using Quine-McClukey tabular method.

Step 1 - Arrange the given min terms in an ascending order and make the groups based on the number of ones present in their binary representations. So, there will be at most 'n+1' groups if there are 'n' Boolean variables in a Boolean function or 'n' bits in the binary equivalent of min terms.

Step 2 – Compare the min terms present in successive groups. If there is a change in only onebit position, then take the pair of those two min terms. Place this symbol '\_' in the differed bit position and keep the remaining bits as it is.

Step 3 - Repeat step2 with newly formed terms till we get all prime implicants.

Step 4 - Formulate the prime implicant table. It consists of set of rows and columns. Prime implicants can be placed in row wise and min terms can be placed in column wise. Place '1' in the cells corresponding to the min terms that are covered in each prime implicant.

Step 5 - Find the essential prime implicants by observing each column. If the min term is covered only by one prime implicant, then it is essential prime implicant. Those essential prime implicants will be part of the simplified Boolean function.

Step 6- Reduce the prime implicant table by removing the row of each essential prime implicant and the columns corresponding to the min terms that are covered in that essential prime implicant. Repeat step 5 for Reduced prime implicant table. Stop this process when all min terms of given Boolean function are over.

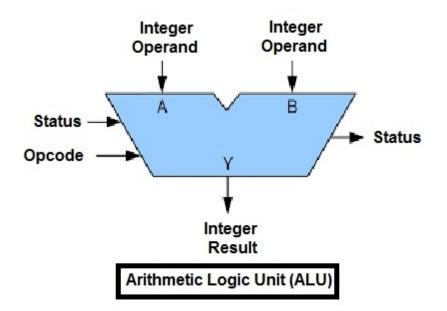

# ALU

An arithmetic logic unit (ALU) is a digital circuit used to perform arithmetic and logic operations. It represents the fundamental building block of the central processing unit (CPU) of a computer. Modern CPUs contain very powerful and complex ALUs. In addition to ALUs, modern CPUs contain a control unit (CU). Most of the operations of a CPU are performed by one or more ALUs, which load data from input registers. A register is a small amount of storage available as part of a CPU. The control unit tells the ALU what operation to perform on that data and the ALU stores the result in an output register. The control unit moves the data between these registers, the ALU, and memory.

ALU is also known as an Integer Unit (IU). The arithmetic logic unit is that part of the CPU that handles all the calculations the CPU may need. Most of these operations are logical in nature. Depending on how the ALU is designed, it can make the CPU more powerful, but it also consumes more energy and creates more heat. Therefore, there must be a balance between how powerful and complex the ALU is and how expensive the whole unit becomes. This is why faster CPUs are more expensive, consume more power and dissipate more heat.

Different operation as carried out by ALU can be categorized as follows -

- logical operations: These include operations like AND, OR, NOT, XOR, NOR, NAND, etc.

- Bit-Shifting Operations: This pertains to shifting the positions of the bits by a certain number of places either towards the right or left, which is considered a multiplication or division operations.

- Arithmetic operations: This refers to bit addition and subtraction. Although multiplication and division are sometimes used, these operations are more expensive to make. Multiplication and subtraction can also be done by repetitive additions and subtractions respectively.

# **Module-III**

# Sequential circuits and systems

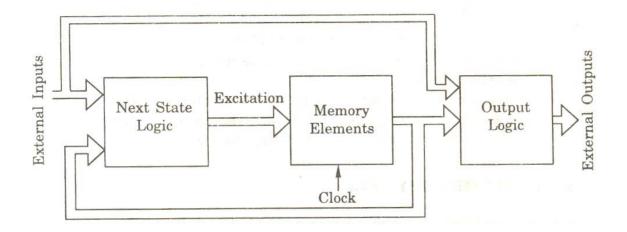

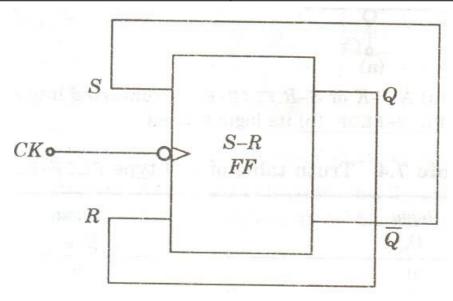

So far we have directed our studies towards the analysis and design of combinational digital circuits. Though very important, it constitutes only a part of digital systems. The other major aspect of digital systems is analysis and design of sequential circuits. However, sequential circuit design depends, to a large extent, on the combinational circuit design discussed earlier. There are many applications in which digital outputs are required to be generated in accordance with the sequence in which the input signals are received. This requirement cannot be satisfied using a combinational logic system. These applications require outputs to be generated that are not only dependent on the present input conditions but they also depend upon the past history of these inputs. The past history is provided by feedback form the output back to the input.

A block diagram of a sequential circuit is shown in Fig. It consists of combinational circuits which accept digital signals from external inputs and from outputs of

memory elements and generates signals for external outputs and for inputs to memory elements referred to as excitation.

A memory element is some medium in which one bit of information (1 or 0) can be stored or retained until necessary, and thereafter its contents can be replaced by a new value. The contents of memory elements in Fig. can be changed by the outputs of the combinational circuit which are connected to its input.

The combinational circuit performs certain operations, some of which are used to determine the digital signals to be stored in memory elements. The other operations are performed on external inputs and memory outputs to generate the external outputs.

The above process demonstrates the dependence of the external outputs of a sequential circuit on the external inputs and the present contents of the memory elements (referred to as the *present state* of memory elements). The new contents of the memory elements, referred to as the *next state;* depend on the external inputs and the present state, hence, the output of a sequential circuit is a function of the time sequence of inputs and the internal states.

Sequential circuits are classified in two main categories, known as *Sychronous* and *Asynchronous* sequential circuits depending on timing of their signals.

A sequential circuit whose behaviour depends upon the sequence in which the input signals change is referred to as an asynchronous sequential circuit. The outputs will be affected whenever the inputs change. The commonly used memory elements in these circuits are time delay devices. These can be regarded as combinational circuits with feedback.

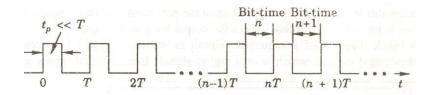

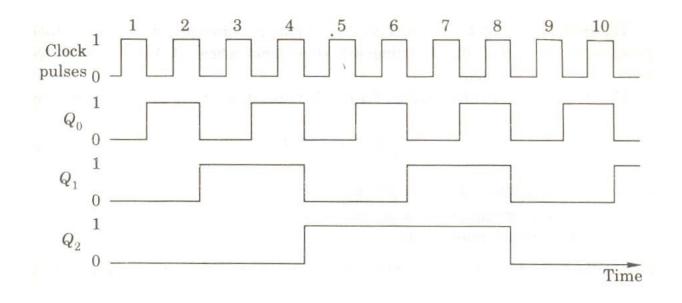

A sequential circuit whose behaviour can be defined from the knowledge of its signal at discrete instants of time is referred to as a synchronous sequential circuit. In these systems, the memory element are affected only at discrete instants of time. The synchronization is achieved by a timing device known as a system clock which generates a periodic train of clock pulses as shown in Fig.below. The outputs are affected only with the application of a clock pulse.

A train of pulses.

Since the design of asynchronous circuits is more-tedious and difficult, therefore their uses are rather limited.

Synchronous circuits have gained considerable domination and wide popularity and are also known as *clocked-sequential circuits*. The memory elements used are FLIP-FLOPs

which are capable of storing binary information.

# 4.1 **1-BIT MEMORY CELL**

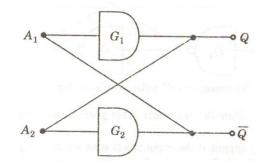

The basic digital memory circuit is known as FLIP-FLOP. It has two stable states which are known as the 1 state and the 0 state. It can be obtained by using NAND or NOR gates. We shall be systematically developing a FLIP-FLOP circuit starting from the fundamental circuit shown in Fig. 7.3. It consists of two inverters  $G_1$  and  $G_2$  (NAND

gates used as inverters). The output of  $G_1$  is connected to the input of  $G_2$  (A<sub>2</sub>) and the output of  $G_2$  is connected to the input of  $G_1$  (A<sub>1</sub>).

Cross- coupled inverters as a memory element.

Let us assume the output of  $G_1$  to be Q = 1, which is also the input of  $G_2$  ( $A_2 = 1$ ). Therefore, the output of  $G_2$  will be Q = 00, which makes  $A_1 = 0$  and consequently Q = 1 which confirms our assumption.

In a similar manner, it can be demonstrated that if Q = 0, then Q = 1 and this is also consistent with the circuit connections.

From the above discussion we note the following

- 1. The outputs Q and  $\overline{Q}$  are always complementary.

- 2. The circuit has two stable states; in one of the stable state Q = 1 which is referred to as the 1 state (or set state) whereas in the other stable state Q = 0 which is referred to as the 0 state (or reset state).

If the circuit is in 1 state, it continues to remain in this state and similarly if it is in 0

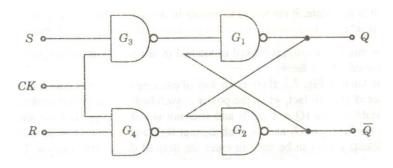

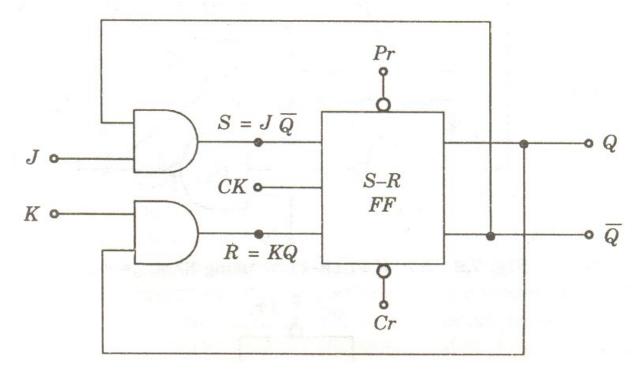

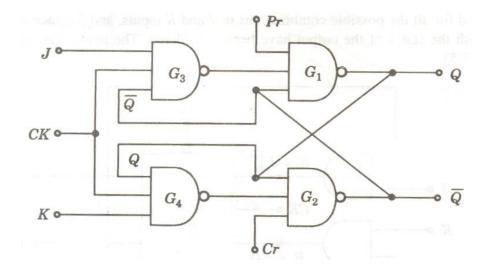

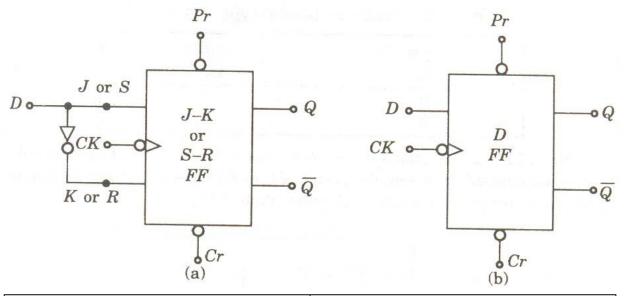

## 4.1 CLOCKED S-R FLIP-FLOP

It is often required to set or reset the memory cell in synchronism with a train of pulses (Fig. known as clock (abbreviated as CK). Such a circuit is shown in Fig., and is referred to as a *clocked set-reset* (S-R) FLIP- FLOP.

A clocked S-R FOIP-FLOP.

In this circuit, if a clock pulse is present (CK = 1), its operation is exactly the same as above. On the other hand, when the clock pulse is not present (CK =0), the gates  $G_3$  and  $G_4$  are inhibited, i.e. their outputs are 1 irrespective of the values of S or R. In other words, the circuit responds to the inputs S and R only when the clock is present.

Assuming that the inputs do not change during the presence of the clock pulse, we can express the operation of a FLIP-FLOP in the form of the truth table in Table 4.1 for the S- R FLIP-FLOP. Here  $S_n$  and  $R_n$  denote the inputs and  $Q_n$  the output during the bit time  $Q_{n+1}$  denotes the output Q after the pulse passes, i.e. in the bit time n + 1.

| Inp | outs           | Output           |

|-----|----------------|------------------|

| Sn  | R <sub>n</sub> | Q <sub>n+1</sub> |

| 0   | 0              | Qn               |

| 1   | 0              | 1                |

| 0   | 1              | 0                |

| 1   | 1              | ?                |

If  $S_n = R_n = 0$ , and the clock pulse is applied, the output at the end of the clock pulse is same as the output before the clock pulse, i. e.  $Q_{n+1} = Q_n$ . This is indicated in the first row of the truth table.

If  $S_n = 1$   $R_n = 0$ , the output at the end of the clock pulse will be 1, where if  $S_n = 0$  and  $R_n = 1$ , then  $Q_{n+1} = 0$ . These are indicated in the second and third rows of the truth table respectively.